九州酷游 九州酷游ku 体育台积电与苹果“对赌”3nm芯片和三星决“生死”

A17 Pro采用了台积电最新的3nm工艺(N3)制造,晶体管数量达到190亿,这是台积电3nm工艺首次应用在顶尖芯片上,而3nm工艺将比5nm工艺的晶体管密度多70%、同等功耗下速度可提升15%,或者同等速度下功耗降低30%。

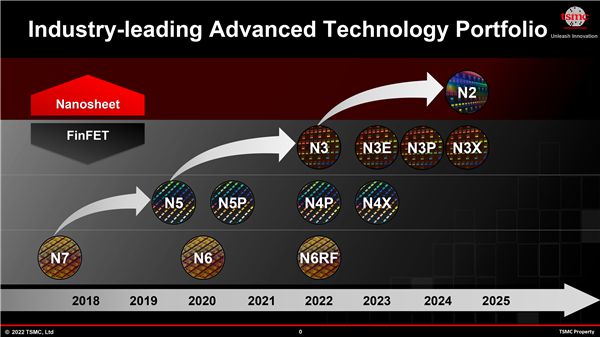

根据台积电的资料,其3nm节点可以分为N3B、N3E、N3P、N3X等,这里的N3B也就是N3,而之所以做了这么多拆分,是因为台积电在不同的技术指标上进行了对应的优化。

图为台积电工艺节点路线工艺,但是它的诞生并非一帆风顺,首先是延期。有消息称苹果原计划是在A16上导入这一节点,换句线首发整整晚了一年。另外,一度有消息称苹果一度计划放弃N3,理由是其能效不达标,而台积电也有意放弃,猜测的理由是缺少核心客户,而事实也是如此,包括像AMD、英伟达、联发科这些企业,也确实都转向了N3E。

更为反常的是,就在新iPhone发布前,一则台积电和苹果签订的“对赌”协议将台积电推向了舆论的焦点。

协议规定,未来一年台积电3nm将只为苹果专用,如果生产的芯片中有不良的废片,将不再按业界惯例由客户(即苹果)埋单,而是由台积电自己消化。据估计,仅仅这一项就能为苹果节省几十亿美元的额外费用。

这次台积电的让步很不寻常,因为苹果将独占目前最先进的台积电的3nm工艺长达一年的时间,这将让苹果的产品更有竞争力。为何台积电肯打破惯例为苹果做出如此大的让步呢?

彼时,苹果也在三星代工生产芯片,但因为双方的智能手机竞争、供应链安全等诸多原因,苹果将越来越多的芯片交给台积电生产。现在,苹果所有的芯片都由台积电代工,并成为了台积电最大的客户。

今年6月,苹果在发布头显Vision Pro的同时发布了两款高性能的芯片M2 max和M2 ultra,采用台积电增强型5nm工艺制造。而更早的M1系列芯片也是由台积电(标准5nm工艺)加工。

而此次台积电为苹果打破惯例的做法,让业界深感意外。有人说台积电已被苹果精准“拿捏”:如果不签这个协议,有可能失去这家占台积电营收1/4的大客户的订单,九州酷游 九州酷游平台没有哪个客户会像苹果那样能对顶尖芯片下如此大的订单。而如果签了,A17 Pro芯片将成为台积电自己手中的“烫手山芋”!

接下来我们会重点的讲一讲为什么A17 Pro会成为“烫手的山芋”,台积电又将如何来解决这个问题。

。一块晶圆片上可以同时制造数百颗同样的裸芯片,之后将晶圆片上的裸芯片切割开来,封装后安装到电子产品上。根据

。但客户也并非完全承担损失,因为有些不良芯片并非完全坏掉了,而只是无法发挥100%的设计性能。只需降低芯片工作频率,其中一部分不良芯片还是可以在低端产品上继续使用的,这样客户也会挽回一部分损失。一般来说,半导体制造业在

,良率能达到99%以上。业内有消息称,这次台积电为苹果iPhone15制造的A17 Pro芯片良率很低,仅达到了70-80%,换句线%的不良芯片买单,我们可以大概算一笔账,看看台积电要花费多少冤枉钱。每片3nm晶圆大约3万美元,不良率按较低的20%计算,每月加工5万片12寸晶圆,那么12个月台积电要为此额外支出费用就是36亿美元(约合人民币260亿元)

如果上述计算符合实际情况,那么如果要扭转这种“巨亏”的局面,台积电唯一能改变的就是良率。

良率不仅决定台积电这一家企业盈亏,也决定了芯片行业能否按照摩尔定律预测的节奏前进,甚至决定了芯片是否能发明出来。

完美地错过了这一载入史册的重大发明,而将芯片的发明拱手让给了当时两家名不见经传的小公司:德州仪器和仙童半导体

当微米尺寸的灰尘落到晶圆表面,就会让当时微米级别的晶体管发生故障。莫顿认为灰尘是平均分布的,但实际上并非如此。可能有些区域没有灰尘,那里的良率可以达到100%。如果把灰尘颗粒比作射出的箭,将硅晶圆比作靶子,晶体管比作靶心,尺寸越小,被灰尘“击中”的概率越低。由于灰尘可能较大,一次损坏多个晶体管,但它们同属于一颗裸芯片,所以只有这一颗芯片被损坏,其他位置的芯片还是好的。这样芯片的良率不是像莫顿估计的那样接近于零。

与莫顿的严密思维相反,那些“不信邪”的小公司德州仪器和仙童半导体等,不断地探索提高芯片良率的方法。

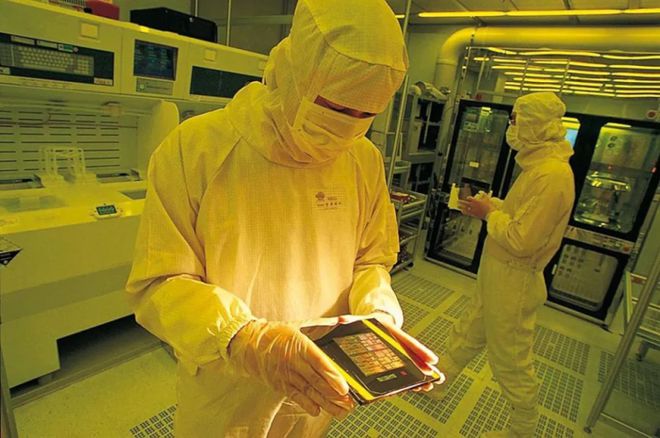

早先,制造厂将芯片制造车间改成成无尘的超净间,通过空气过滤系统使得超净间比医院的手术室还要干净1000倍以上

还远远不够,当前先进工艺车间,几乎已经看不到操作员,只有机器人和机械臂在全自动地完成各项操作

台积电超净间的工程师,数据显示硕士毕业生新入职年薪可达到45.5万元。

对良率最有发言权的莫过于台积电的创始人张忠谋。张忠谋早年加入德州仪器时,负责半导体制造业务,为IBM代工的电晶体,当时的良率只有2%-3%,而在张忠谋的操刀之下,这一良率提升至20%以上,超过客户IBM自有产线。后来张忠谋回忆,自己“立了大功,被公司送到斯坦福念博士”,解决良率问题,应是其在德州仪器“大功”之一。

良率决定了芯片的成本,而成本下降的速度决定了芯片更新换代的快慢,即摩尔定律的节奏

当前,九州酷游 九州酷游平台一整块制成的晶圆已经高达数万美元,良率稍有降低,就会急剧提升成本,所以业界对良率的追求变得更加急迫。

提高良率的一个新趋势是采用更小的裸芯片。还是射箭的例子,如果将中10环靶心比作裸芯片,同样的,裸芯片面积越小,被损害的概率也越小,小芯片技术(chiplet)应运而生——将一大块裸芯片拆分成许多小芯片,让每颗小芯片的面积更小,良率提高。然后再将许多小芯片在硅晶圆以及基板上封装在一起,做出一块更大的芯片。

2个月前,有消息称台积电3nm工艺的良率仅为55%,最新消息是70-80%,这是一个不错的进步。如果在未来的几个月内,台积电能继续将良率提高到90%甚至95%以上,废片带来的成本问题就会大幅降低。